En el ámbito de los modernos sistemas de radar y transceptores inalámbricos, el rendimiento de los lazos de fase fraccional-N (PLL) juega un papel crucial. Estos PLL son componentes esenciales que ayudan en la síntesis, modulación y sincronización de señales oscilantes. Sin embargo, un problema común que afecta a los PLL es la presencia de señales no deseadas conocidas como espuelas fraccionarias. Estas espuelas pueden provocar errores y degradación en el rendimiento general de los sistemas, afectando diversas tecnologías como vehículos autónomos, sistemas de vigilancia y comunicaciones más allá de la era 5G.

Para abordar el desafío de minimizar las espuelas fraccionarias en los PLL de fase fraccional-N, investigadores del Instituto de Tecnología de Tokio han desarrollado dos técnicas de diseño innovadoras. La primera técnica implica el uso de un divisor fraccional en cascada, que divide la palabra de control de frecuencia (FCW) en dos valores que están lejos de ser un número entero. Al implementar este método, los investigadores lograron filtrar componentes de alta frecuencia de forma natural sin necesidad de distorsión digital previa (DPD), simplificando así el proceso de diseño y mejorando la velocidad de bloqueo de fase. La segunda técnica propuesta por el equipo de investigación gira en torno a un convertidor digital a tiempo pseudo-diferencial (DTC) para superar las limitaciones de las implementaciones estándar de DTC. Al utilizar dos DTC de rango medio con las mismas integralidades no lineales pares y simétricas en el funcionamiento diferencial, los investigadores lograron cancelar las INL a través de la resta en el detector de fase del PLL. Este enfoque innovador condujo a una reducción significativa en las espuelas fraccionarias y mejoró el rendimiento general del jitter del PLL.

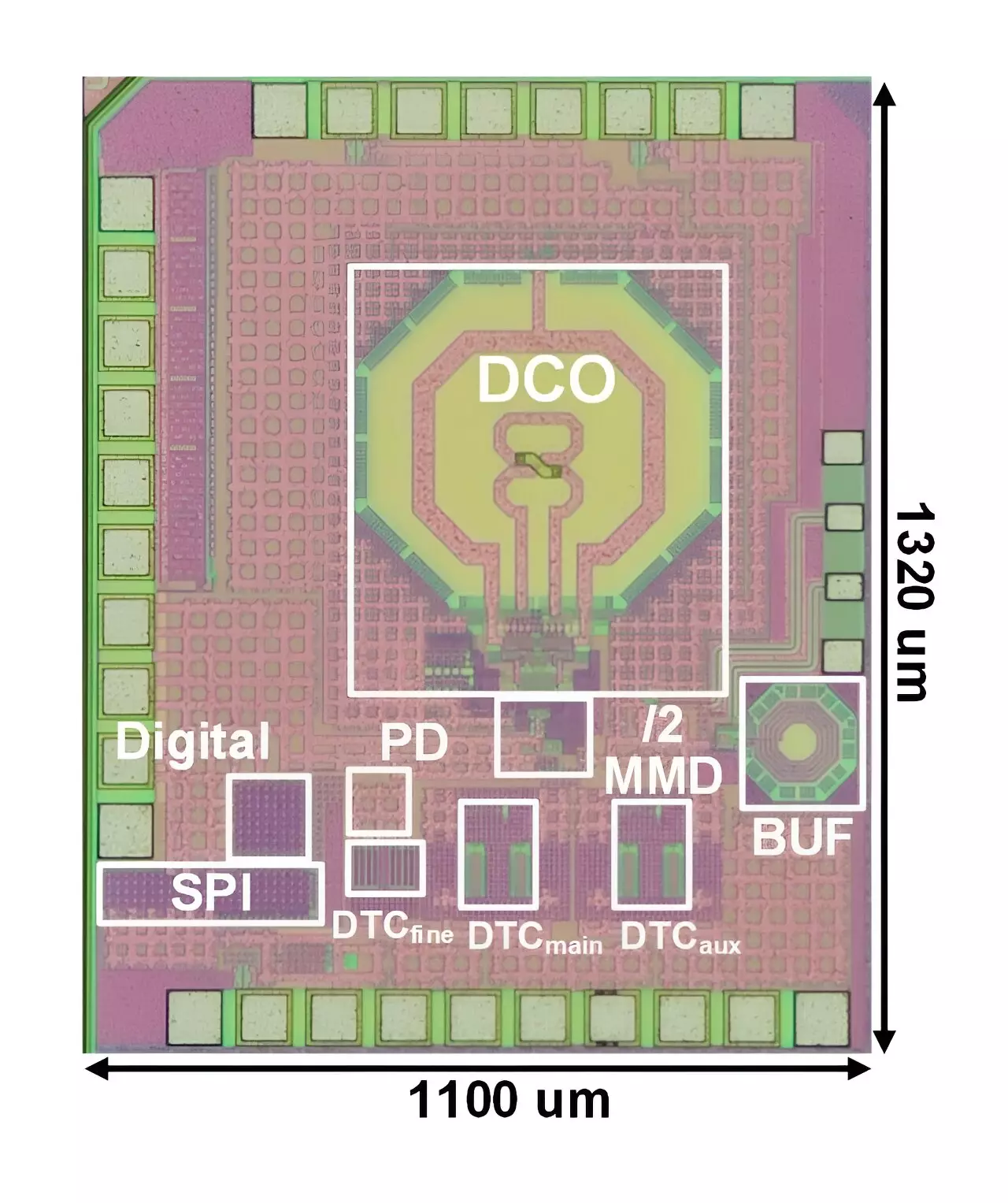

El equipo de investigación probó sus conceptos de diseño implementando el PLL digital propuesto mediante un proceso de CMOS de 65 nm, que requirió un área de circuito activo mínima de solo 0.23 mm². Comparando el rendimiento de su dispositivo con los diseños existentes de última generación, los investigadores observaron varias ventajas. Al suprimir eficazmente las espuelas fraccionarias, el jitter integrado del PLL se redujo de 243.5 fs a 143.7 fs, marcando una mejora significativa en el rendimiento. El profesor Kenichi Okada, que lidera el equipo de investigación en Tokio Tech, resaltó la importancia del divisor fraccional en cascada propuesto y de las técnicas de DTC pseudo-diferencial para lograr la clase más baja de jitter sin necesidad de tecnología DPD. Este diseño innovador tiene el potencial de revolucionar diversas aplicaciones donde los PLL de fase fraccional-N se utilizan comúnmente, allanando el camino para avances tecnológicos en comunicaciones inalámbricas, vehículos autónomos, sistemas de vigilancia y más allá.

Las técnicas de diseño innovadoras desarrolladas por los investigadores del Instituto de Tecnología de Tokio han establecido un nuevo estándar para los lazos de fase fraccional-N. Al abordar el problema de las espuelas fraccionarias mediante el uso de un divisor fraccional en cascada y un DTC pseudo-diferencial, el equipo de investigación ha demostrado una mejora significativa en el rendimiento del PLL. Este avance puede tener implicaciones de largo alcance para las futuras tecnologías que dependen de los PLL, contribuyendo a avances en comunicaciones inalámbricas, sistemas autónomos y aplicaciones más allá de la era 5G.

Deja una respuesta