Los ordenadores cuánticos tienen el potencial de superar a los ordenadores convencionales en algunas tareas, incluyendo problemas de optimización complejos. Sin embargo, los ordenadores cuánticos también son vulnerables al ruido, lo que puede resultar en errores computacionales. Los ingenieros han estado tratando de idear enfoques de computación cuántica tolerantes a fallos que podrían ser más resistentes al ruido y, por lo tanto, podrían escalarse de manera más robusta. Un enfoque común para lograr la tolerancia a fallos es la preparación de estados mágicos, que introducen las llamadas puertas no-Clifford. Investigadores de la Universidad de Ciencia y Tecnología de China, el Laboratorio Clave de Henan de Información Cuántica y Criptografía y el Laboratorio Nacional Hefei demostraron recientemente la preparación de un estado mágico lógico con fidelidad más allá del umbral de destilación en un procesador cuántico superconductor. Su artículo, publicado en Physical Review Letters, describe una estrategia factible y efectiva para generar estados mágicos lógicos de alta fidelidad, un enfoque para realizar la computación cuántica tolerante a fallos.

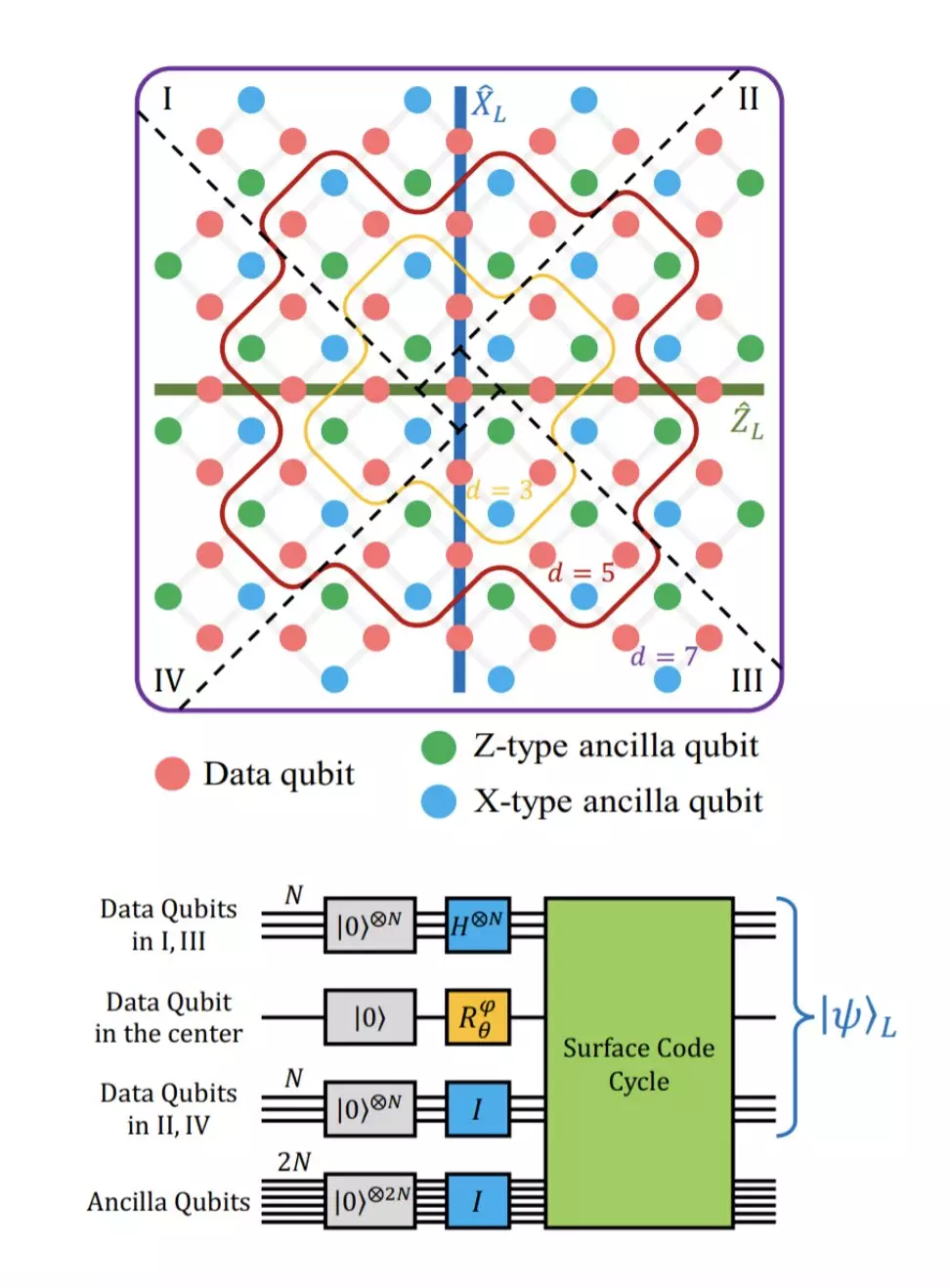

El objetivo final de la investigación reciente del profesor Zhu y sus colegas es realizar una computación cuántica robusta, tolerante a fallos y universal. La preparación de estados mágicos lógicos es un paso clave para implementar puertas lógicas no-Clifford, que a su vez conducen a la consecución de la computación cuántica tolerante a fallos. El profesor Zhu explicó: «En términos sencillos, la idea básica de nuestro protocolo es inyectar primero el estado a preparar en uno de los qubits del código de superficie, y luego ‘propagar’ la información del estado a todo el código de superficie, logrando así una preparación de estado lógico. En este protocolo, la elección de la posición de inyección del estado a preparar y los estados de inicialización de los otros qubits es importante».

El protocolo propuesto por este equipo de investigadores describe una estrategia simple, experimentalmente factible y escalable para preparar estados mágicos sin procesar de alta fidelidad en procesadores cuánticos superconductores. Como parte de su estudio reciente, el profesor Zhu y sus colegas aplicaron este protocolo en Zuchongzhi 2.1, un procesador cuántico de 66 qubits con un diseño de acoplamiento ajustable. «El diseño de este procesador nos permite manipular la interacción entre cualquier par de qubits adyacentes, asegurando que nuestras compuertas cuánticas tengan una suficiente alta fidelidad a pesar de un alto grado de paralelismo», dijo el profesor Zhu. «Este diseño también es propicio para expandir la escala de qubits en un solo procesador».

Cuando los investigadores implementaron su protocolo en el procesador Zuchongzhi 2.1, lograron resultados muy prometedores. Específicamente, prepararon de manera no destructiva tres estados mágicos lógicos con fidelidades lógicas de 0.8771±0.0009, 0.9090±0.0009 y 0.8890±0.0010, respectivamente, que son mayores que el umbral de protocolo de destilación de estados, 0.859 (para el estado mágico de tipo H) y 0.827 (para el estado mágico de tipo T). «Hemos logrado un hito crítico en el desarrollo de la computación tolerante a fallos basada en el código de superficie al preparar con éxito un estado mágico lógico de distancia tres con una fidelidad que supera el umbral de destilación», dijo el profesor Zhu. «Este resultado implica que podemos alimentar estados mágicos de baja fidelidad al circuito de destilación de estados mágicos, someterlos a múltiples destilaciones para obtener estados mágicos lo suficientemente altos en fidelidad y luego utilizarlos para construir compuertas lógicas no-Clifford tolerantes a fallos».

En el futuro, el protocolo desarrollado por el profesor Zhu y sus colegas podría ser utilizado por otros equipos de investigación para lograr estados mágicos lógicos sin procesar de alta fidelidad, utilizando una gama más amplia de procesadores cuánticos superconductores. En última instancia, podría contribuir a la realización de la computación cuántica tolerante a fallos, lo que a su vez permitiría el desarrollo de ordenadores cuánticos de mayor escala. El profesor Zhu agregó: «En el campo de la corrección de errores cuánticos, planeamos seguir explorando dos direcciones principales de investigación. En primer lugar, nuestro objetivo es mejorar el rendimiento de un qubit lógico (o memoria cuántica corregida de errores) reduciendo la tasa de error de manipulación física y aumentando el número de qubits codificados, de manera que se pueda suprimir la tasa de error lógico a niveles prácticos.

Deja una respuesta